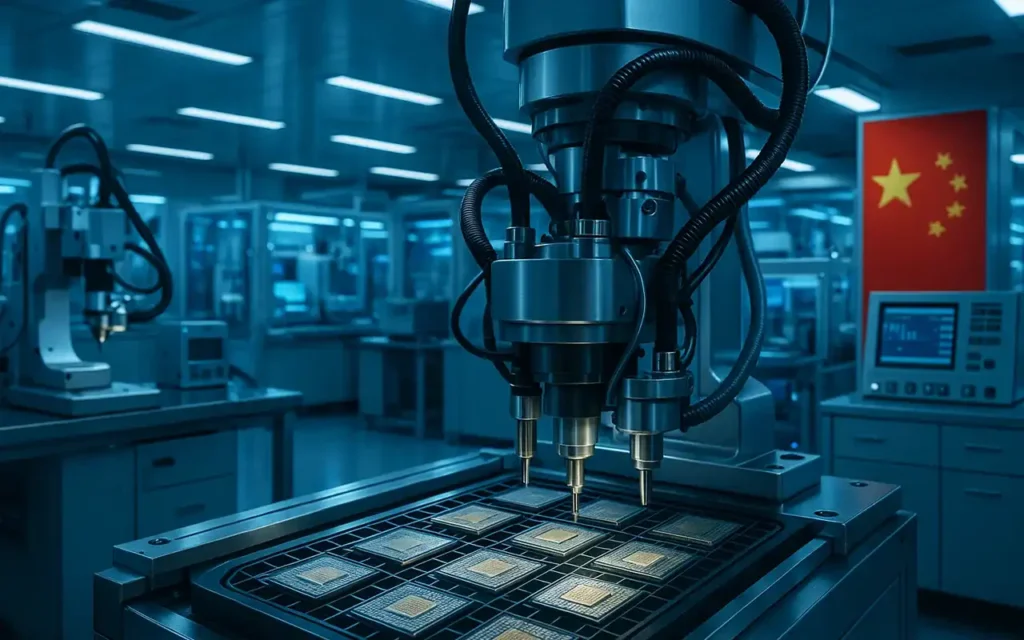

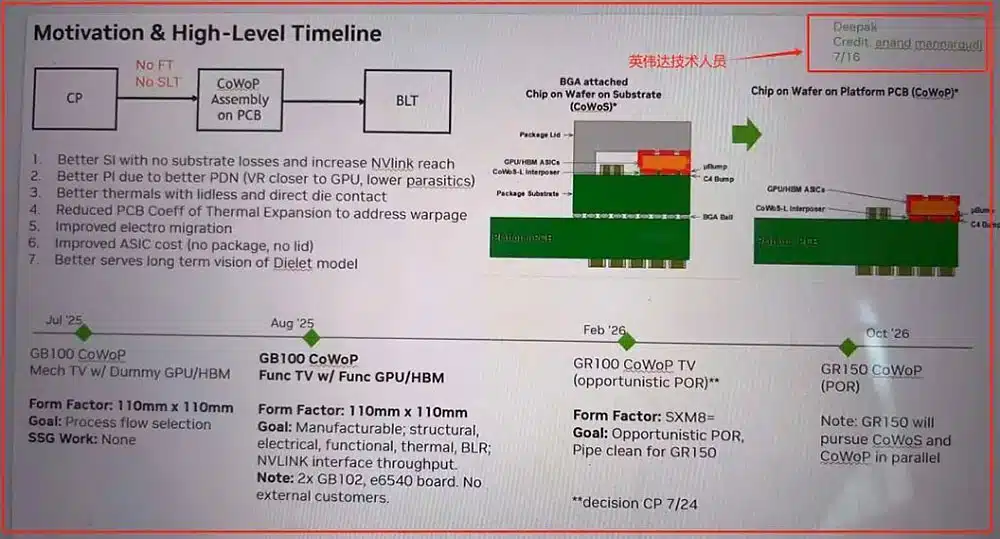

En el siempre cambiante tablero del hardware, China acaba de mover ficha con una propuesta que podría sacudir los cimientos del packaging de chips tal como lo conocemos. Su nombre es CoWoP (Chip on Wafer on PCB) y, aunque suene técnico, lo que plantea es claro: reducir costes, simplificar el ensamblaje y escalar producción sin depender de los sustratos ABF que hoy dominan el sector.

Una jugada que nadie vio venir… y que ya inquieta a TSMC e Intel

Hasta ahora, TSMC con su CoWoS y Intel con Foveros y EMIB llevaban la delantera en la carrera por interconectar los cerebros de nuestros PCs, consolas y servidores de IA. Pero CoWoP llega para romper esquemas. Su propuesta elimina directamente el uso de sustratos intermedios, montando los chips directamente sobre la placa (PCB) mediante un sistema de microprotuberancias y capas conductoras que asumen parte del trabajo que antes estaba reservado a componentes mucho más caros.

Y lo más llamativo: se apoya en líneas de producción ya maduras de PCBs, lo que abre la puerta a un abaratamiento considerable en costes y tiempos.

¿Revolución o solo humo made in China?

Aunque sobre el papel suena a revolución, en la práctica los desafíos son enormes. Para que un PCB haga de sustrato avanzado, se necesita una precisión de fabricación milimétrica. Hablamos de pistas de 10 micras o menos, algo que solo unas pocas fábricas en el mundo pueden lograr con consistencia industrial.

Además, los gigantes del sector como NVIDIA no parecen apresurados por adoptar esta solución. De momento, CoWoP está más cerca de ser una apuesta estratégica china para ganar protagonismo en el sector de servidores de IA que una amenaza directa a los líderes actuales.

Un guiño al futuro con ADN de Intel y TSMC

Lo interesante es que CoWoP no nace de la nada. Toma ideas de los enfoques de Intel y TSMC, pero les da un giro más agresivo en cuanto a coste y producción. Si logran resolver los obstáculos técnicos —y no es poca cosa—, podríamos estar ante una nueva etapa en la evolución del empaquetado avanzado. Una especie de “modo turbo” para ensamblar chips que podrían alimentar desde centros de datos hasta dispositivos de IA más ligeros y asequibles.